学习价值。

学习价值。

关键词:DDS;可控增益;幅频特性

1 总体设计

本系统针对当前幅频测试装置对可控成本的亟需采用了基于AD9851芯片的信号发生器,在1MHz到40MHz频率范围内,生成1MHz步进的信号,使其通过AD603放大器进行A/D转换,在嵌入式异构计算ICORE平台上,结合FPGA高性能处理性能,实现并行FFT运算,再与ARM配合组成双核心系统板,对信号进行处理,顯示出信号随频率变化的规律,最后传送到示波器中,显示输出信号的幅频特性。

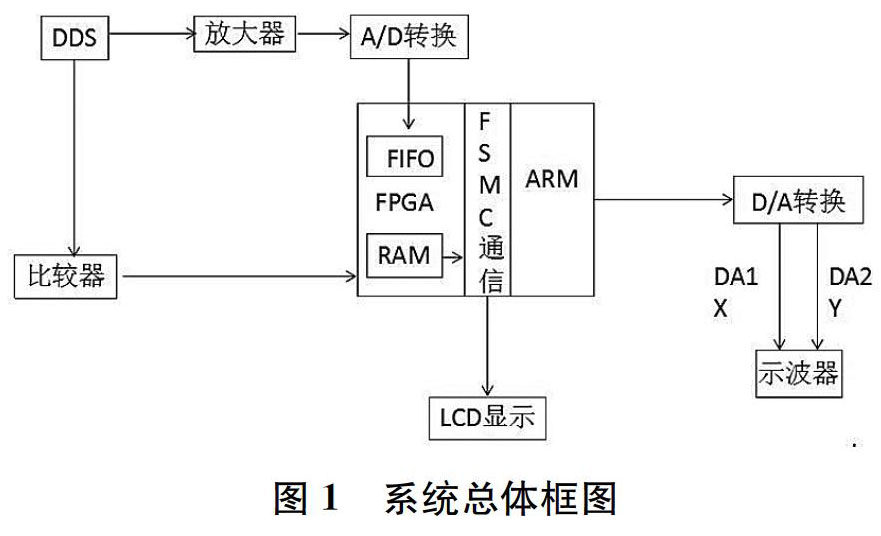

整体方案采用扫频法。其原理为使信号源输出的频率按特定规律自动连续并且周期性重复,利用双核心系统板将输出送到示波器上显示,从而得到幅频特性曲线。该方案不会出现频率点离散而遗漏细节的问题,并且得到的是动态频率特性,更符合实际应用。其总体框图如图1所示。

2 硬件电路设计

2.1 信号发生器电路分析与设计

信号发生器电路主要由两部分组成:AD9851核心电路和七阶无源滤波器电路。下面分别介绍这两部分电路。

2.1.1 AD9851核心电路分析与设计

AD9851核心电路中DDS芯片以稳定度高的参考时钟为参考源,通过精密的相位累加器和数字信号处理,通过高速D/A变换器产生所需的正弦波。在本电路中,输出电流IOUT1和IOUT2引脚并接电位器到地,使AD9851正弦波输出幅值可以满足要求,通过改变可变电阻阻值即可改变输出电压值。

2.1.2 七阶无源滤波器分析与设计

七阶无源低通滤波器能够有效抑制DDS的输出杂散,滤除杂波得到有用的信号。其设计原理如下:

①根据所需的截止频率,计算M的值:M=所需截止频率/归一化截止频率。

②由M的值算电路所需的电感和电容值:L(new)=L(old)/M,C(new)=Cold) /M。

③根据所需特征阻抗算得K值:K=待设计滤波器特征阻抗/归一化滤波器特征阻抗。

④由K值求得最终的电感和电容值:L= L(new)×K,C=C(new) /K。

根据以上步骤,以特征阻抗50Ω,截止频率77MHz,可算得所需满足的低通滤波器的元件值。

2.2 放大器电路分析与计算

AD603带内纹波较大,而两级级联时最大增益可达60dB,因此,模块中在两级AD603中间加了低通滤波器使通带内平坦。为拓宽其增益范围及带宽范围,本电路最后一级设计了放大电路,通过改变电阻值就可以改变其放大倍数,从而提高输出电压值。电路框图如图2所示。

该放大电路由射极跟随器AD603放大电路和增益控制电路组成,下面分别介绍这三部分电路。

2.2.1 电压跟随器

为满足放大器输入阻抗的要求,在放大电路前端设计一个电压跟随器,实现输入阻抗匹配。

2.2.2 AD603电路

AD603放大电路由两级程控放大及末级增益放大组成,为了使通带内输出平坦,在第一级和第二级之间加入低通滤波器。两级AD603的控制模式都选择90MHz带宽模式,按照官方芯片手册的连接方式来设计电路,两级AD603的增益控制引脚直接短接,实现增益的同步设置。末级放大器连接方式为同相输入比例放大,其增益由电阻的比值来确定。

2.2.3 增益控制电路

由于AD603的有效增益控制范围有限,故可通过调节电位器的阻值来控制所需的电压值,使VG的变化范围达到所需要求。

2.3 幅频特性测试装置

用STMF103和CycloneIV EP4CE622C8双核心系统板作为该幅频特性测试装置。将数据输入控制模块的6位输出地址作为ROM输入数据缓存,此时的输出即为FFT输入信号的实部。经过ROM控制模块得到FFT的全部输入信号,输入IP核中进行傅立叶变换。

3 程序的设计

AD9851内部含有高速、高性能的10位D/A转换器,可用作全数字编程的频率合成器,可产生稳定、纯净的正弦波,其产生正弦波的流程图如图3所示。

软件流程图如图4所示,系统首先时钟初始化,AD采样电路开始采样前端放大电路的输出信号,由于FFT运算模块和采样模块速率差别很大,因而选用一个FIFO缓冲,采样完毕的数据输入FPGA内FIFO缓存,FIFO写满后依次输出到FFT IP核运算,运算成功则将频率及幅值信息保存在ROM中,并且给ARM输出中断信号,运算失败则返回至FFT IP核的调用。ARM这边收到FPGA发出的中断信号,调用终端服务程序,从FPGA的ROM中读取频率及幅值信息。

在本设计中,控制及计算部分都由FPGA来实现。其中Nios核完成键盘控制,液晶显示、FFT算法实现、功率计算、周期性判断及失真度测量的功能;而自动增益控制、A/D转换控制以及数字滤波器则由VHDL语言实现,以减轻CPU的负担,同时两部分并行处理提高了系统的速度。

4 结语

文章自主研究并设计出一种可远程显示信号幅频特性的测试装置,在硬件上集中分析了放大电路、增益控制电路、滤波电路等电路设计;在软件上,采用FP-GA+ARM异构设计,在FPGA中输入FIR)、调用IP核、实现FFT运算对信号进行快速处理,经过FSMC总线连接ARM进行控制和幅频特性显示。整套装置设计原理较为创新,实现效果比较理想,可以很好的运用于课题学习制作中。

参考文献

[1]方华.一种远程幅频特性测试装置的设计[J].科技创新导报,2017,14(28):1-2.

[2]许赛男.幅频特性的数学分析[J].信息化研究,2005, 31(12):16-19.

[3]叶先万,蒋碧波,李跃伟.一种智能无线充电系统设计[J].计算机测量与控制,2018,(6).

[4]王宏蕊,李向国,白海海,等.一种远程幅频特性测试仪的设计[J].兰州文理学院学报(自然科学版),2018,(3).